In ASIC Physical Design, mitigating IR drop (voltage drop due to resistance in power delivery networks) is critical for power integrity. Here are key power reduction methods used for achieving a better PPA and to help close on the IR drop limits, along with practical implementations:

1. Power Grid Optimization

A. Mesh Density Enhancement

- Technique: Increase width/spacing of power rails and straps.

- Impact: Reduces resistance ((R = \rho \cdot L/A)) in high-current regions.

- Tool Command (Cadence Innovus):

set_power_ring_strategy -nets {VDD VSS} -width 2um -spacing 1umB. Decoupling Capacitors (Decaps)

- Technique: Place decaps near high-switching logic (e.g., clock buffers, ALUs).

- Impact: Local charge reservoirs suppress transient IR drop.

- Implementation:

add_decaps -cell DECAP_1UM -density 5% -region {x1 y1 x2 y2}

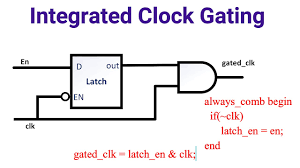

2. Clock Domain Optimization

A. Clock Gating

- Technique: Disable clock trees for idle logic blocks.

- Impact: Reduces dynamic power (switching activity) → lowers peak current.

- Example:

insert_clock_gating -gate_type ICG -threshold 10

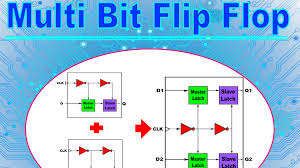

B. Multi-Bit Flip-Flop (MBFF) Merging

- Technique: Combine single-bit FFs into multi-bit FFs.

- Impact: Fewer clock buffers → lower clock network power.

- Tool Command:

set_optimize_registers -merge_flops true

3. Logic & Placement Strategies

A. Voltage Scaling

- Technique: Use Multi-Vt libraries:

- LVT (Low-Vt) for critical paths.

- HVT (High-Vt) for non-critical paths to reduce leakage.

- Impact: Balances performance and IR drop.

- Command:

set_leakage_optimization true -power_driven trueB. Dynamic Voltage Frequency Scaling (DVFS)

- Technique: Adjust voltage/frequency based on workload.

- Impact: Lowers average current demand.

- Implementation: Requires power switches and adaptive clocking.

4. Routing & Signal Integrity

A. Shielding High-Speed Nets

- Technique: Route critical nets (clocks) between VDD/VSS.

- Impact: Reduces crosstalk-induced current spikes.

- Command:

shield_net -net CLK -shield_net VSS -width 0.5umB. Staggered Buffer Insertion

- Technique: Insert buffers in staggered phases.

- Impact: Smoothes di/dt (current slew rate) to avoid IR spikes.

- Example:

set_buffer_opt_strategy -stagger_insertion true5. Advanced Techniques

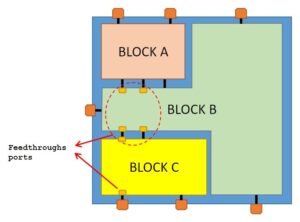

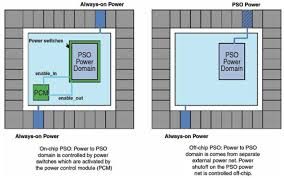

A. Power Gating

- Technique: Use header/footer switches to shut off power to idle blocks.

- Impact: Eliminates leakage but requires wake-up time.

- Implementation:

insert_power_switch -name PSW -control_signal SLEEP -header

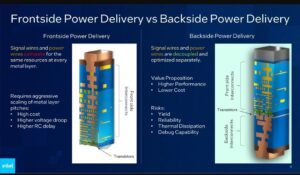

B. TSV Redundancy (3D ICs)

- Technique: Add redundant Through-Silicon Vias (TSVs).

- Impact: Reduces resistance in vertical power delivery.

- Analysis:

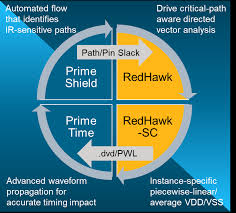

analyze_3dic_power -tsv_resistance 0.01 -tier 26. IR-Aware Timing Closure

A. Voltage-Aware STA

- Technique: Use PrimeTime-SI with voltage derating.

- Impact: Accounts for IR drop in timing signoff.

- Command:

set_voltage_derate -drop 0.9V -corner worstB. ECO Fixes

- Technique: Resize cells or add buffers in IR-drop hotspots.

- Example:

eco_add_buffer -cell BUF_X2 -location {x y} -net VDD7. Toolflow for IR Closure

A. RedHawk/Voltus Analysis

# Ansys RedHawk

redhawk_analyze -ir_drop -dynamic -scenario worst_caseB. Power-Aware Place & Route

# Cadence Innovus

set_power_opt_mode -place true -route true

Key Takeaways

- Preventive Measures: Optimize power grid and decap early.

- Dynamic Reduction: Clock gating, MBFF merging.

- Signoff Correlation: Voltage-aware STA and EM checks.

Example Interview Q&A:

Q: “How would you fix IR drop in a CPU block?”

A:

“First, I’d analyze RedHawk reports to identify hotspots. For localized drop, I’d add decaps and widen power straps. For global drop, I’d implement clock gating and use HVT cells in non-critical paths. Finally, I’d validate with voltage-aware STA.”