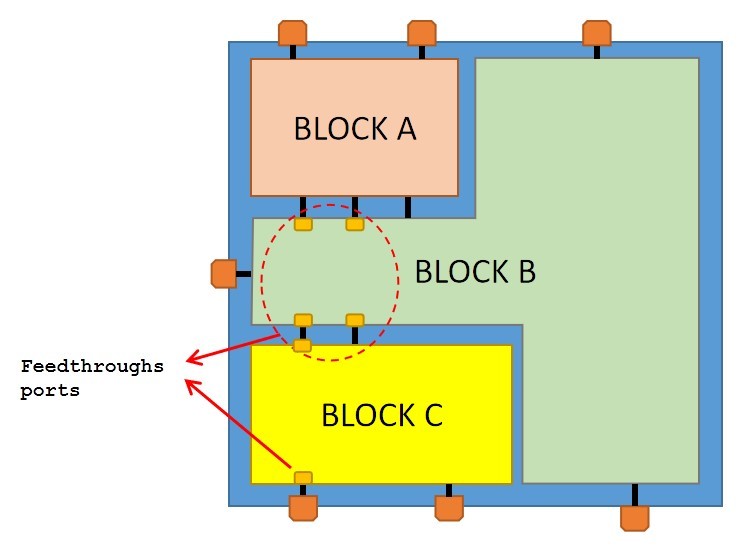

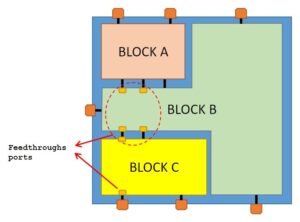

ASIC Low Power Physical Design: Inserting FeedThroughs:

Ever wonder how complex Feedthrough signals are routed between two Hard Macros when propagating through collapsible blocks, while navigating the challenges of meeting STA timing, routing congestion and UPF constrains with isolation cells?

Here’s a simplified and structured approach on the basics of how to handle domain crossings for feedthrough buffers in collapsible power domains while ensuring always-on (AON) buffer placement.

We will refer to Synopsys Fusion Compiler commands for this example.

Key Steps Explained

- Layer Selection: Use upper metals (e.g.,

M4/M5) for feedthroughs to avoid block-level routing. - Blockage Alignment: Ensure feedthroughs don’t overlap macros or power straps.

- Hierarchical Flow: Save feedthroughs in DEF for top-level integration.

Port Creation:

create_portadds feedthrough ports at the boundaries ofBlock_AandBlock_B.-direction inoutallows bidirectional signal flow (adjust if unidirectional).

Net Creation:

create_netdefines the feedthrough net and connects ports across blocks.

Buffering:

insert_bufferprevents signal degradation over long distances (critical for timing).

Handling Power State Conflicts

Routing Constraints:

set_feedthrough_strategyreserves metal layers (e.g.,M4) to avoid congestion.

Legalization:

- Ensures feedthroughs don’t violate placement/routing rules.

Verification:

report_net and check_connectivity validate the feedthrough path.

Here’s a TCL script for Synopsys Fusion Compiler to insert feedthrough ports and nets between Block_A and Block_B during floorplanning, ensuring clean signal routing across hierarchical boundaries:

1. Script to Create Feedthrough Ports and Nets

#!/usr/bin/env tclsh

# Load the design and floorplan

read_db -technology "tech.tf"

read_verilog "design.v"

link_design -top "TOP"

# Define block boundaries (adjust coordinates as needed)

set blockA_bbox {100 100 300 400} ;# Block_A: x1 y1 x2 y2

set blockB_bbox {500 100 700 400} ;# Block_B: x1 y1 x2 y2

# Create feedthrough ports on Block_A and Block_B

create_port -direction inout -bbox $blockA_bbox FT_AtoB

create_port -direction inout -bbox $blockB_bbox FT_BtoA

# Create feedthrough net and connect ports

create_net -net_type feedthrough FT_NET

connect_net -net FT_NET -ports {FT_AtoB FT_BtoA}

# Add buffers to prevent signal degradation

insert_buffer -net FT_NET -cell BUF_X2 -location [expr [lindex $blockA_bbox 0] + 50] [expr [lindex $blockA_bbox 1] + 50]

# Reserve routing tracks for feedthrough (e.g., Metal4)

set_feedthrough_strategy -nets FT_NET -layers {M4} -width 0.2 -spacing 0.5

# Legalize placement to avoid DRCs

legalize_placement -nets FT_NET

# Verify feedthrough connectivity

report_net -nets FT_NET -verbose

check_connectivity -nets FT_NET

# Save floorplan changes

write_def -output "feedthrough_def.def"

write_verilog -output "feedthrough_netlist.v"

2. Advanced Enhancements

A. Timing-Driven Feedthroughs

# Set max delay constraint for feedthrough net

set_max_delay -from [get_ports FT_AtoB] -to [get_ports FT_BtoA] 1.5 -datapath_only

# Optimize feedthrough path

psynopt -nets FT_NET -effort highB. Power-Aware Routing

# Shield feedthrough to reduce noise

set_feedthrough_strategy -nets FT_NET -shield_net VSS -shield_width 0.1C. Automated Feedthrough Insertion

# Loop to create multiple feedthroughs

foreach net {data1 data2 clk} {

create_port -direction inout -bbox $blockA_bbox FT_${net}_A

create_port -direction inout -bbox $blockB_bbox FT_${net}_B

create_net -net_type feedthrough FT_${net}

connect_net -net FT_${net} -ports [list FT_${net}_A FT_${net}_B]

}3. Verification Commands

# Check feedthrough timing

report_timing -from FT_AtoB -to FT_BtoA

# Verify DRCs

verify_drc -nets FT_NET

# Report congestion near feedthroughs

report_congestion -area [list $blockA_bbox $blockB_bbox]Verification Commands for AON FT buffering though collapsible domains:

# Check AON buffer placement

report_power_domain -cells [get_cells -filter “ref_name=~BUF_X1_AON*”]

# Verify domain crossings

check_power_domains -nets $feedthrough_nets -verbose

# Timing checks (AON buffers should not be gated)

report_timing -from [get_pins -of [get_cells -filter “ref_name==BUF_X1_AON”]*/A] \

-to [get_pins -of [get_cells -filter “ref_name==BUF_X1_AON”]*/Z]

4. Key Considerations

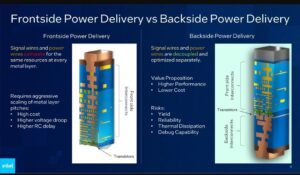

Library Cells: Use AON-specific buffers (marked -always_on in the library).

Placement: Keep AON buffers near domain boundaries to minimize wire length.

Routing: Use non-collapsible power rails (e.g., VDD_AON) for AON buffers.

Q: “How do you ensure feedthroughs don’t worsen congestion?”

Reserve dedicated metal layers (e.g., M4) for feedthroughs using set_feedthrough_strategy, analyze congestion with report_congestion, and avoid high-density regions.

If needed, I adjust placement blockages.

Q: “What if the feedthrough net fails timing?”

“Insert buffers (BUF_X2) and set_max_delay constraints. For critical nets, use wider metal layers or shield with VSS to reduce crosstalk.”

Q: “What if the AON buffer fails timing?”

“Size up the buffer (BUF_X2_AON) or adjust placement to reduce wire delay. For critical paths, use set_max_delay to prioritize domain-crossing nets.”

Q: “How do you ensure feedthrough buffers stay always-on?”

“Tag them with -power_domain PD_AON during insertion and verify via report_power_domain. The UPF file enforces -always_on for PD_AON.”

AON Buffer Insertion Strategy for inserting feedthrough signals through a collapsible domain.

A. Identify Feedthrough Signals Crossing Domains

# Get all feedthrough nets between Block_A (collapsible) and Block_B (AON)

set feedthrough_nets [get_nets -of [get_pins -filter "full_name=~Block_A*||full_name=~Block_B*"]]B. Insert AON Buffers for Domain Crossing

foreach net $feedthrough_nets {

# Check if net crosses power domains (collapsible ↔ AON)

set driver_pd [get_power_domain -of [get_drivers $net]]

set load_pd [get_power_domain -of [get_loads $net]]

if {($driver_pd != $load_pd) && ($driver_pd == "PD_CPU" || $load_pd == "PD_CPU")} {

# Insert AON buffer (ensure it's in PD_AON)

set buf_cell "BUF_X1_AON" ;# Library cell with AON attribute

set buf_loc [get_location -median $net] ;# Place near domain boundary

insert_buffer -net $net -cell $buf_cell -location $buf_loc \

-power_domain PD_AON -placement_guide AON_REGION

# Connect buffer output to AON domain

connect_net -net $net -ports [get_pins -of [get_cells -filter "ref_name==$buf_cell"]]

}

}C. Define Placement Guides for AON Buffers

# Create an AON buffer region near the domain boundary

create_placement_blockage -name AON_REGION -bbox {x1 y1 x2 y2} -type partial

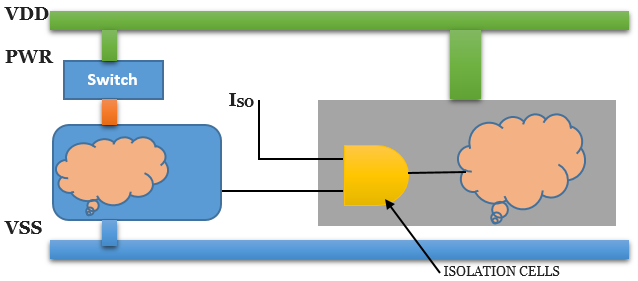

set_app_options -name plan.pgroute.power_domain_aware -value trueHandling Power State Conflicts

A. Isolation Cell Insertion (Optional)

If feedthrough signals need isolation when the collapsible domain is off:

set_isolation -domain PD_CPU -isolation_power_net VDD_AON \

-isolation_ground_net VSS -clamp_value 0 \

-applies_to outputsB. Level Shifter Insertion (Voltage Crossing)

If domains operate at different voltages:

insert_level_shifter -net $net -from PD_CPU -to PD_AON \

-location $buf_loc -cell LVL_SHIFT_AONUPF/CPF Constraints Example

Ensure UPF/CPF defines PD_AON as always-on:

create_power_domain PD_AON -elements [list BUF_X1_AON*] -always_on

create_power_domain PD_CPU -shutoff_condition {!PWR_EN}