ASIC Physical Design Engineers play a critical role in PPA (Power, Performance, Area) recovery throughout the RTL-to-GDSII flow.

Below is a structured breakdown of their key tasks and techniques for PPA optimization, categorized by Power, Performance, and Area:

- Dynamic Power Reduction

Clock Gating:

Insert clock gating cells (ICGs) to disable clocks for idle logic blocks.

Example: Automate gating with TCL scripts in synthesis/PnR tools.

- Multi-Bit Flip-Flop (MBFF) Merging:

Combine single-bit FFs into multi-bit FFs to reduce clock network power.

Tool: Synopsys DC/ICC2 set_clock_gating_options.

- Voltage Scaling:

Implement Multi-Vt libraries (LVT for critical paths, HVT for non-critical).

Challenge: Balancing timing vs. leakage power

- Voltage Scaling:

2. Leakage Power Reduction

- Power Gating:

Use header/footer switchesto shut off power to idle blocks (e.g., sleep transistors). Example: Automated power switch insertion in Cadence Innovus.

Body Biasing:

Apply reverse body bias (RBB) to HVT cells to further reduce leakage.

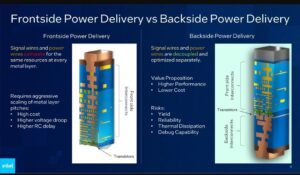

3. IR Drop Mitigation

- Decoupling Capacitors:

Add decap cells near high-switching logic (e.g., CPU cores).

Tool: RedHawk/Voltus for decap placement analysis.

- Power Mesh Optimization:

Increase metal width/pitch in high-current regions.

AWS Example: Graviton chips use hierarchical power grids.

2. Performance Optimization

A. Timing Closure

Useful Skew:

- Deliberately imbalance clock tree latency to improve setup/hold margins.

- Tool: PrimeTime + ECO scripts.

Critical Path Optimization: - Cell Sizing: Upsize drivers on critical paths.

- Buffer Insertion: Break long nets to reduce RC delay.

Example:tcl resize_cell -lib_cell BUF_X4 [get_cells critical_path_ff]

B. Clock Tree Synthesis (CTS)

H-Tree Structures:

- Balance clock skew for high-frequency designs (e.g., AWS Graviton).

Clock Mesh: - Use mesh networks for ultra-low skew in multi-GHz designs.

C. Crosstalk Mitigation

- Shielding:

Route critical nets (clocks) between VDD/VSS lines.

Tool: Innovusadd_shield

Spacing Rules:

Increase spacing for high-aggressor nets.

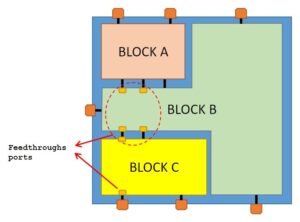

3. Area Recovery

A. Congestion Reduction

- Macro Placement:

Place macros at chip edges to reduce routing congestion.

Example: Use Cadence Innovusplan_design - Cell Padding:

Add whitespace around high-density cells.

B. Logic Optimization

Library Cell Selection

- High-Density Libraries:

Use low-drive cells in non-critical paths.

Tradeoff: Timing vs. area.

4. Toolflows & Automation

A. PPA-Aware Scripting

- TCL/Python for ECOs:

# Example: Auto-resize cells with negative slack

foreach cell [get_cells -filter "slack < 0"] {

resize_cell -lib_cell BUF_X4 $cell

}- Machine Learning:

- Use ML-based tools (e.g., Synopsys DSO.ai) for PPA exploration.

B. Signoff Correlation

- Cross-Tool Validation:

- Compare power/timing between PrimeTime (signoff) and PnR tools.