In ASIC physical design, congestion occurs when there are more routing demands than available resources (tracks) in a region, leading to routing failures, increased delays, and DRC violations. Managing congestion is crucial for achieving a routable design with optimal performance.

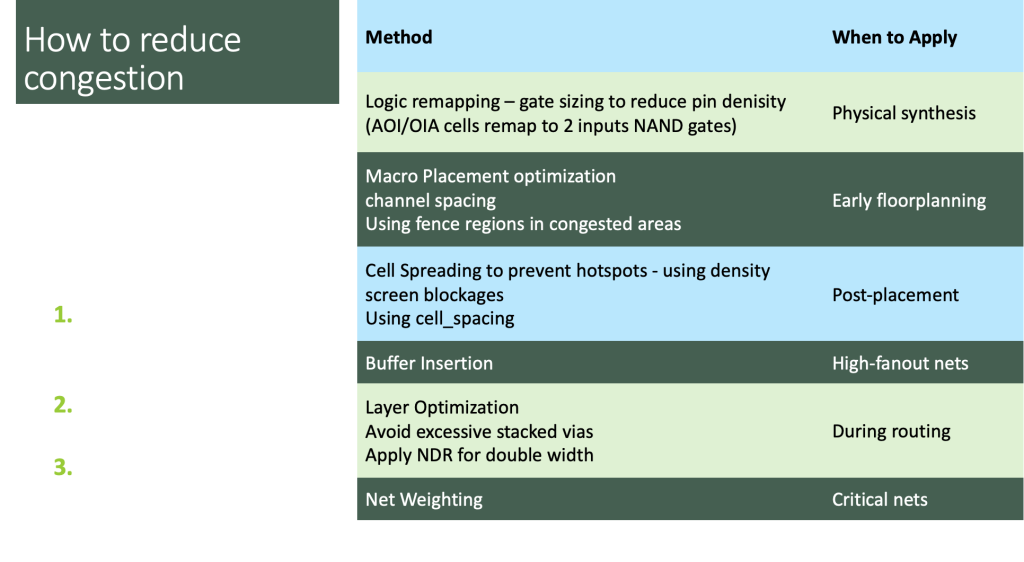

Methods to Reduce Congestion

1. Floorplanning Techniques

Macro Placement Optimization

-

- Place large macros (RAMs, CPUs) at the periphery to free up routing channels.

-

- Avoid placing macros in high-density standard cell regions.

-

- Use channel spacing between macros for smoother routing.

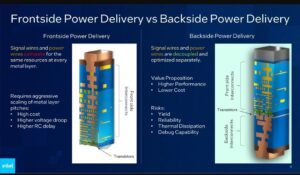

Power Grid Planning

-

- Avoid overly dense power stripes that block routing tracks.

-

- Use staggered power stripes instead of continuous ones.

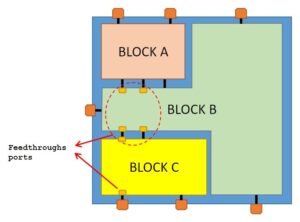

Hierarchical Floorplanning (Block-Level)

-

- Divide the design into sub-blocks with controlled interconnect density.

-

- Use fence regions to restrict cell placement near congested areas.

2. Placement Optimization

Cell Spreading

-

- Increase cell spacing in congested regions (e.g.,

setPlaceMode -place_global_cell_spacingin Cadence Innovus).

- Increase cell spacing in congested regions (e.g.,

-

- Use density screens (

-uniformDensity) to prevent hot spots.

- Use density screens (

- Utilization Control

Keep standard cell utilization ≤ 70-80% in congested areas.

-

- Use partial placement blockage to restrict cell density.

Congestion-Driven Placement

-

- Run global placement with congestion awareness (e.g.,

-timingDriven -congEffort high).

- Run global placement with congestion awareness (e.g.,

-

- Use ECO placement to redistribute cells post-optimization.

3. Routing Strategies

Layer Assignment

-

- Route local nets on lower metals (M1-M3) and global nets on higher metals (M4+).

- Avoid excessive via stacking in dense regions.

Track Utilization Balancing

-

- Use alternate routing directions (e.g., M1: Horizontal, M2: Vertical).

-

- Avoid routing bottlenecks by spreading signals across layers.

Non-Default Rules (NDR)

-

- Use double-width spacing for critical nets to reduce conflicts.

-

- Apply shielding for noise-sensitive nets to prevent detours.

4. Logic & Netlist Optimizations

Buffer & Inserter (Buf/Inv) Tree Balancing

-

- Reduce fanout congestion by inserting buffers in high-fanout nets.

-

- Use clock tree synthesis (CTS) optimizations to minimize skew-induced congestion.

Logic Restructuring

-

- Replicate high-fanout cells to distribute load.

-

- Split long wires with repeaters to reduce routing pressure.

Net Weighting

-

- Assign higher priority to timing-critical nets (

setNetWeight).

- Assign higher priority to timing-critical nets (

5. Physical Synthesis & ECO Fixes

Congestion-Aware Synthesis

-

- Use physical synthesis tools (e.g., Fusion Compiler, Genus iSpatial) to optimize for routability.

-

- Apply gate sizing to reduce cell density.

-

- Post-Route ECOs

-

- Perform minor placement legalization to relieve congestion.

-

- Reroute problematic nets with manual guidance.

6. Advanced Techniques

Pin Access Optimization

-

- Use offset pins or middle-of-line (MOL) routing to ease pin access.

-

- Avoid pin congestion by spreading pins in macros.

DFM (Design for Manufacturability) Adjustments

-

- Follow metal density rules to avoid CMP (Chemical Mechanical Polishing) issues.

-

- Use fill cells to maintain uniform density.

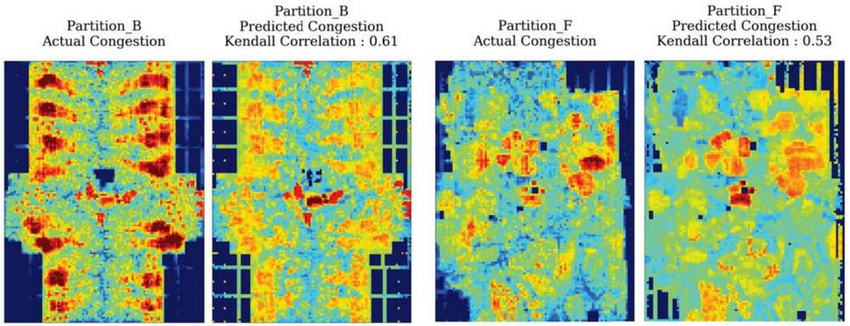

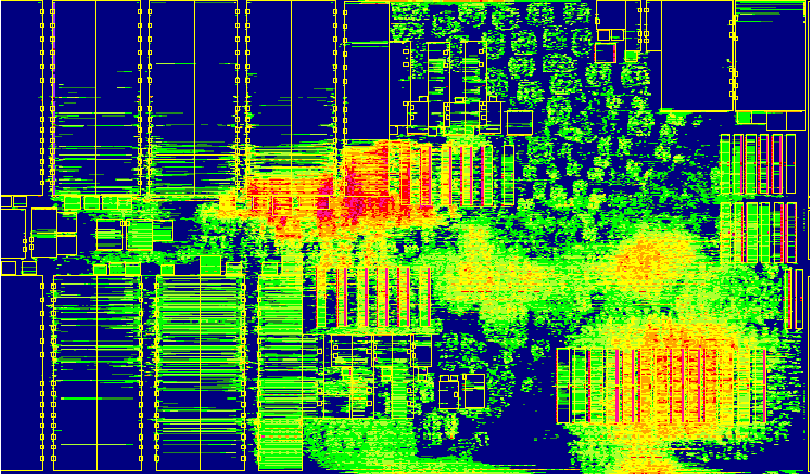

Congestion Analysis & Debugging

Early-Stage Checks:

-

- Use global routing congestion maps (e.g., in Innovus, ICC2).

-

- Identify hotspots (red/yellow zones) in congestion reports.

Metrics to Monitor:

-

- Overflow (%): Percentage of unroutable nets.

-

- Cell Density: Should be < 80% in most regions.

-

- Track Utilization: Should not exceed 90%.

Common Fixes:

-

- If congestion is localized: Adjust placement, add routing blockages.

-

- If global: Reduce utilization, optimize netlist.

Example Flow for Congestion Reduction

-

- Initial Floorplan → Identify congestion hotspots.

-

- Adjust Macro Placement → Free up routing channels.

-

- Run Congestion-Aware Placement → Spread cells uniformly.

-

- Optimize Power Grid → Avoid blocking routing tracks.

-

- Rerun Routing & Verify → Check overflow reduction.

Summary

| Method | When to Apply | Impact |

|---|---|---|

| Macro Placement | Early floorplanning | High (reduces routing blocks) |

| Cell Spreading | Post-placement | Medium (improves track usage) |

| Buffer Insertion | High-fanout nets | Medium (reduces net crowding) |

| Layer Optimization | During routing | High (better resource usage) |

| Net Weighting | Critical nets | Low (prioritizes key routes) |

Final Tip: Use iterative refinement—congestion fixes often require multiple placement/routing trials.