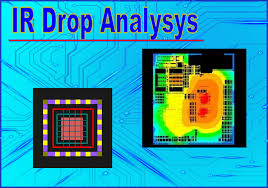

Contrary to the popular belief, High IR drop is not just a setup timing problem anymore, which can be solved by cranking up the PMIC voltages during silicon on-die testing.

Yes, it is true that high IR drop can cause hold timing violations leading to functional failures. IR drop failures on clock paths must be analyzed and violating instances fixed before shipping the GDS2 to the foundry.

High IR drop can cause hold timing violations on timing paths in ASIC designs. Here’s how it happens and how to mitigate it:

How high IR Drop Affects Hold Timing which can cause functional failures:

Voltage-Dependent Delay:

-

- Lower voltage (due to IR drop) increases gate delay, as there is an increase in the transition times and slew rates of signal and clock waveforms.

-

- Hold time is checked at the same clock edge, so slower cells (from IR drop) can fail to capture data before the next edge.

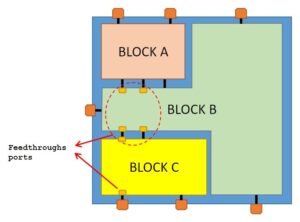

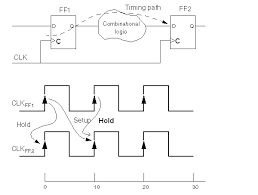

Path-Specific Impact:

-

- Hold violations occur on short paths where data arrives too early.

-

- If the launch flip-flop (FF) is in an IR-drop hotspot, its clock-to-Q delay increases, while the capture FF (with normal voltage) clocks data too soon → hold violation.

Clock vs. Data Path Asymmetry:

- If clock buffers in the capture path suffer IR drop but data path buffers do not, the clock edge is delayed relative to data → hold risk.

Example Scenario

- Launch FF: In an IR-drop zone (0.9V instead of 1.0V).

- Capture FF: At full voltage (1.0V).

Effect:

- Launch FF’s clock-to-Q delay increases by ~10–20% (due to lower voltage).

- Data arrives later at the capture FF, but the capture clock is faster → hold violation.

Mitigation Techniques

1. IR Drop-Aware Timing Signoff

-

- Use voltage-aware STA (PrimeTime-SI) with derating:

set_voltage_derate -early 0.9 -late 1.0 # Early path = worst-case hold-

- RedHawk/Voltus generates voltage maps for SPICE-accurate delay calculation.

2. Hold Fixes for IR-Drop Hotspots

-

- Insert Buffers on short paths:

eco_add_buffer -cell BUF_X2 -location {x y} -hold_fix-

- Increase Delay with high-Vt cells or delay cells in non-critical paths.

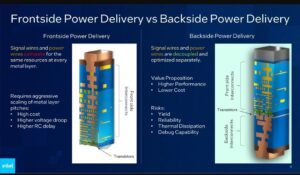

3. Power Grid Hardening

-

- Add Decaps near timing-critical FFs:

add_decaps -cell DECAP_1UM -density 10% -near_objects [get_cells FF_*]-

- Widen Power Straps in high-current regions:

set_power_ring_strategy -width 3um -spacing 2um4. Clock Tree Optimization

-

- Balance Skew: Ensure IR drop affects clock paths uniformly.

-

- Shield Clock Nets: Reduce noise-induced jitter.

shield_net -net CLK -shield_net VSSToolflow for IR-Drop-Aware Hold Closure

-

- Analyze IR Drop:

redhawk_analyze -ir_drop -dynamic -scenario worst_case-

- Generate Voltage-Derated Constraints:

generate_voltage_aware_sdc -voltage_map ir_drop.map-

- Run STA with Derating:

prime_time -voltage_aware -hold-

- ECO Fixes:

eco_hold_fix -use_high_vt -buffer_cells BUF_X2Key Takeaways

-

- IR drop increases cell delays, worsening hold timing.

-

- Critical Areas: Launch FFs in IR-drop zones, asymmetric clock/data paths.

-

- Solutions: Voltage-aware STA, decaps, buffer insertion, and power grid fixes.

Here is a TCL snippet to automate hold fixes in IR-drop hotspots

#!/usr/bin/env tclsh

# Step 1: Load IR drop analysis data (from RedHawk/Voltus)

set ir_drop_map [read_voltage_map "ir_drop.map"] # Format: {cell_name voltage}

# Step 2: Identify cells in IR-drop hotspots (e.g., voltage < 90% of nominal)

set hotspot_cells {}

foreach {cell voltage} $ir_drop_map {

if {$voltage < 0.9} { # Assuming 1.0V nominal

lappend hotspot_cells $cell

}

}

# Step 3: Find hold violations near hotspots

set hold_vios [get_timing_violations -type hold -margin 0.1] # 100ps margin

set critical_vios {}

foreach vio $hold_vios {

set cell [get_attribute $vio endpoint]

if {[lsearch $hotspot_cells $cell] != -1} {

lappend critical_vios $vio

}

}

# Step 4: Apply fixes (buffers, cell sizing, decaps)

foreach vio $critical_vios {

set path [get_attribute $vio path]

set endpoint [get_attribute $vio endpoint]

set startpoint [get_attribute $vio startpoint]

# Fix 1: Insert buffer on the short path

set buf_loc [get_location $endpoint]

insert_buffer -cell BUF_X2 -location $buf_loc -net [get_nets -of $endpoint]

# Fix 2: Replace endpoint FF with high-Vt version to increase delay

if {[is_flip_flop $endpoint]} {

size_cell -cell $endpoint -lib_cell FF_HVT

}

# Fix 3: Add decap near the endpoint

add_decaps -cell DECAP_1UM -near_objects $endpoint -density 5%

}

# Step 5: Verify fixes

report_timing -from $startpoint -to $endpoint -hold