Conformal LEC compares RTL vs. Netlist or Pre-Post P&R Netlists to ensure functional equivalence.

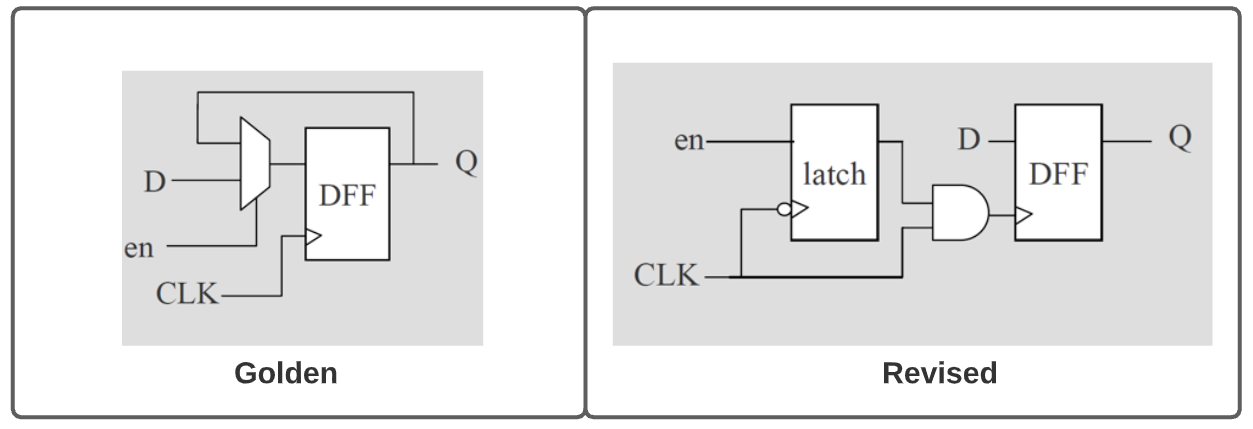

This is how golden DFF vs. revised DFF looks after power optimization.

Common Causes of Conformal LEC (Logic Equivalence Check) Failures in ASIC Physical Design

Conformal LEC compares RTL vs. Netlist or Pre-Post P&R Netlists to ensure functional equivalence.

Failures indicate mismatches—here are the most frequent culprits:

1. Unintended Logic Transformations

Causes:

- Optimization Aggressiveness: Synthesis/P&R tools merge/remove redundant logic.

- Clock Gating/Power Gating: Missing constraints cause gating logic mismatches.

- Constant Propagation: Unintended optimization of tied-high/low signals.

Debug Steps:

# Check if constants are propagated differently:

report_constant -pre_synth vs. report_constant -post_phys2. Clock Tree Modifications

Causes:

- Clock Buffers/Inverters Inserted: CTS alters clock paths (e.g., balancing skew).

- Clock Gating Cells: Added post-synthesis but not modeled in reference design.

Fix:

# Exclude clock cells from LEC:

set_ignore -type cell {CLK_BUF* CLK_INV*}3. Scan Chain Reordering

Causes:

- DFT Insertion: Scan flops reordered for routing efficiency.

- Test Mode Signals: Missing constraints for scan-enable (

SE)/test clocks.

Debug:

# Compare scan chains pre/post-P&R:

report_scan_chain -pre_synth

report_scan_chain -post_phys4. Power-Aware Optimizations

Causes:

- Level Shifters/Isolation Cells: Added for UPF/CPF power domains.

- Retention Registers: Power-gating changes flop behavior.

Fix:

# Map power-aware cells correctly:

set_mapping -match_by_name -type level_shifter5. ECO Changes Not Back-Annotated

Causes:

- Manual ECOs: Logic fixes in P&R not reflected in reference netlist.

- Metal-Only ECOs: Functional changes missed in LEC.

Debug:

# Check ECO log files:

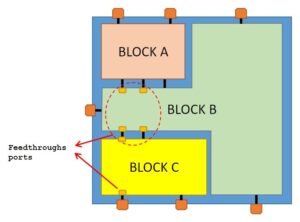

compare_eco -pre_eco netlist.v -post_eco netlist_eco.v6. Black Boxes/Unmodeled Hierarchies

Causes:

- Third-Party IPs: Missing/outdated behavioral models.

- Analog Blocks: Treated as black boxes in RTL but instantiated in netlist.

Fix:

# Define black boxes explicitly:

set_blackbox -module {ADC_CORE PLL_CORE}7. Timing-Driven Optimizations

Causes:

- Gate Sizing: Changes cell drive strength but not functionality.

- Buffer Insertion: Adds delay buffers on critical paths.

Debug:

# Ignore non-functional buffers:

set_ignore -cell_type {BUF*}8. Reset Signal Handling

Causes:

- Asynchronous vs. Sync Resets: Synthesis converts one to the other.

- Reset Tree Buffering: Physical design adds buffers to reset nets.

Fix:

# Align reset policies:

set_reset -sync -all9. Name Mismatches After P&R

Causes:

- Hierarchical Flattening: Physical design removes hierarchies.

- Renaming for DRC: Tools rename cells/nets to avoid violations.

Debug:

# Use signature-based matching:

set_compare -signature10. Missing or Incorrect Constraints

Causes:

- Undefined Don’t-Cares: Unconstrained signals optimized differently.

- False Paths/Multicycle Paths: Not synchronized between RTL and P&R.

Fix:

# Reapply constraints in Conformal:

read_sdc -both pre_synth.sdc post_phys.sdcDebug Flow for LEC Failures

- Isolate Failure Points:

report_failing_points -summary- Compare Hierarchies:

report_design -compare- Check Mapped/Unmapped Logic:

report_unmapped -verbose- Verify Clock/Reset Domains:

report_clock -all

report_reset -allKey Takeaways

| Issue Category | Tool Command | Solution |

|---|---|---|

| Clock Tree Changes | set_ignore -cell CLK_* | Exclude CTS buffers. |

| Scan Chain Reorder | report_scan_chain | Align DFT constraints. |

| Power-Aware Cells | set_mapping -type level_shifter | Map UPF/CPF cells. |

| ECO Mismatches | compare_eco | Back-annotate ECOs. |