OPEN ROAD: Automating RTL-to-GDS Layout Generation

Democratizing Hardware Design

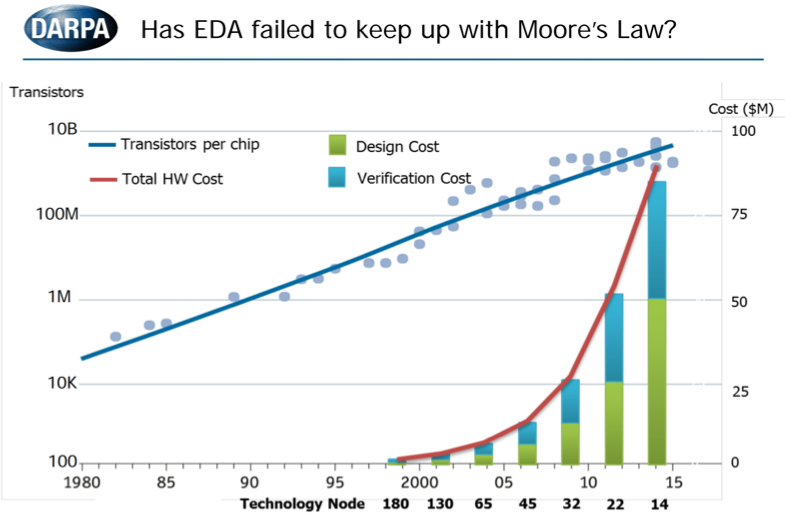

The OpenROAD™ project attacks the barriers of Cost, Expertise and Uncertainty (i.e., Risk) that block the feasibility of hardware design in advanced technologies.

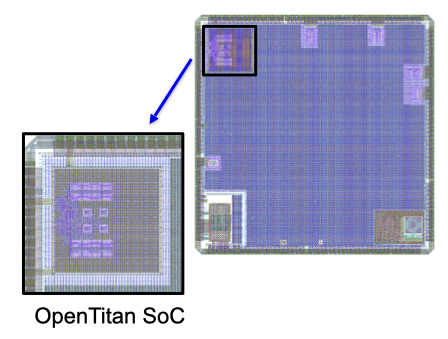

The OPEN ROAD project is an open-source initiative aimed at revolutionizing chip design by providing a fully automated RTL-to-GDS (Register Transfer Level to Graphic Data System) flow. The goal is to make advanced semiconductor design accessible to everyone, from researchers to startups, by eliminating licensing costs and reducing manual intervention.

Key Tools in OPEN ROAD

OPEN ROAD integrates three powerful open-source tools to streamline the entire chip design process:

1. Yosys (RTL Synthesis)

- Role: Converts high-level RTL (Verilog) into a gate-level netlist.

- Features:

- Logic synthesis and optimization.

- Supports multiple FPGA and ASIC flows.

- Extensible with plugins for advanced optimizations.

2. OpenROAD (Place & Route)

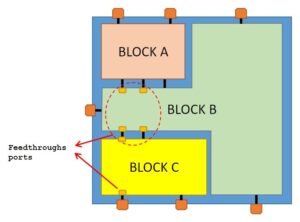

- Role: Takes the synthesized netlist and performs floorplanning, placement, clock tree synthesis (CTS), and routing.

- Features:

- Automated macro placement and power grid generation.

- Timing-driven optimizations.

- Supports advanced nodes (down to 7nm with partner PDKs).

3. Magic (Layout & DRC)

- Role: Used for final layout generation and design rule checks (DRC).

- Features:

- Interactive GDSII editing.

- Detailed DRC validation.

- Supports multiple fabrication technologies.

Why OPEN ROAD Matters

- No Licensing Costs: Unlike commercial tools, OPEN ROAD is entirely free and open-source.

- End-to-End Automation: Reduces human effort in chip design, making it faster and more reliable.

- Accessibility: Enables startups, academics, and hobbyists to design custom chips without expensive EDA tools.

Conclusion

The OPEN ROAD project is a game-changer in semiconductor design, combining Yosys, OpenROAD, and Magic to deliver a seamless RTL-to-GDS flow. By democratizing chip design, it accelerates innovation and lowers barriers to entry in hardware development.

Want to try it out? Check out the project here: https://theopenroadproject.org/

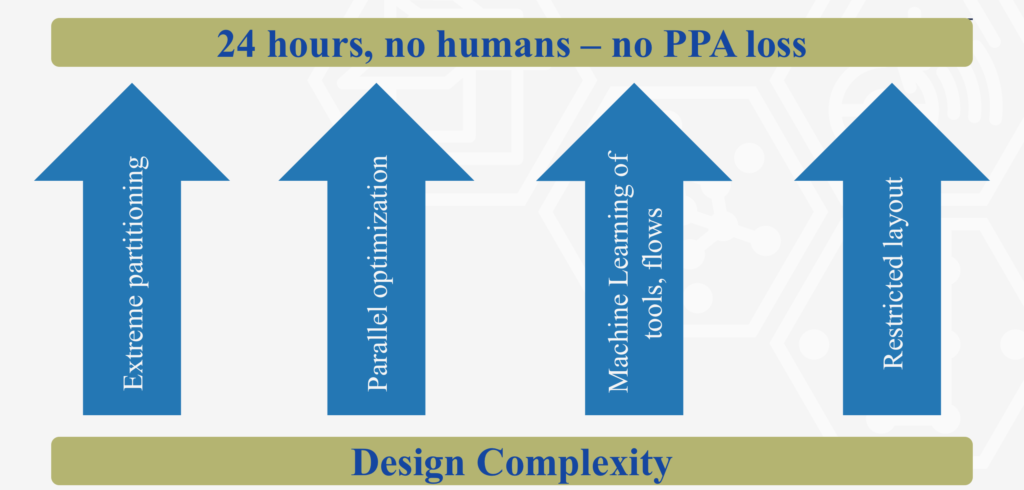

THE PROBLEM

OUR APPROACH

- No Humans: tools must adapt and self-tune, must never get stuck unexpectedly

- 24 hours: extreme partitioning of problems

- parallel search on cloud

- machine learning for predictability

- Mantra: Correctness and safety by construction

- Mantra: Embrace freedom from choice

- Mantra: Often, only one thread needs to succeed